微机原理总结

8086寄存器结构

通用寄存器组

| AH | AL | AX | 累加器 |

|---|---|---|---|

| BH | BL | BX | 基数 |

| CH | CL | CX | 计数 |

| DH | DL | DX | 数据 |

| SP | 堆栈指针 |

|---|---|

| BP | 基址指针 |

| SI | 源变址 |

| DI | 目的变址 |

其他

| IP | 指令指针 | |

|---|---|---|

| FH | FL | 状态标志 |

| CS | 代码段寄存器 |

|---|---|

| DS | 数据段寄存器 |

| SS | 堆栈段寄存器 |

| ES | 附加段寄存器 |

汇编指令

一些默认

- 执行指令后,dst中存放运算结果

- 一个单元(nn)给字时,为nn和nn+1

寻址方式

寻得操作数来源

固定寻址

操作数地址被隐含于操作码中,无需计算EA

立即数寻址

操作数直接放在指令字段中,执行时直接从此读取

显然,由于其无法存放运算结果,故只能作为原操作数使用

寄存器寻址

使用CPU内部寄存器中数据作为操作数

CPU内部执行,无需总线周期

存储器寻址

一般位于DS、SS、ES中,需EU计算出EA,再由BIU计算出PA,通过PA取得操作数

src和dst只能有一个为存储器操作数

直接寻址

直接给出EA(nn)

?S: [nn]

段首址缺省值DS

寄存器间接寻址

EA于寄存器(BX\SI\DI\BP)中,其中BX、SI、DI段首址缺省DS,BP缺省SS

寄存器相对寻址

加上偏移量

AREA[SI]

缺省同上

基址变址寻址

基址加上变址,缺省同上

相对基址加变址寻址

超级加倍

串寻址

隐含使用SI(指向源串首字)、DI

SB或SW(字串)

32为寻址

变址乘了一个比例系数,其他不变,寄存器名称变(前面加个E)

I/O端口寻址

直接端口寻址

端口数0~255

寄存器间接端口寻址

端口数大于255的,放在一寄存器中转借一下

8086指令系统

| im | 立即数 |

|---|---|

| reg | 寄存器 |

| seg | 段寄存器 |

| m | 存储单元 |

CS、IP两个寄存器不做dst

Data Transfer

通用传输

| MOV | im到seg、seg到seg、m到m🙅 |

|---|---|

| XCHG | 交换两操作数内容,im、seg🙅,必有一个reg |

| PUSH | 用于程序保护,不对字节操作(对字,高位先入 |

| POP | 用于恢复数据,同上(SP自动加2 |

累加器专用

| IN | 只能用于AX/AL,tx |

|---|---|

| OUT | 中间寄存器只能使用DX,ts |

| XLAT | (BX+AL)➡️ AL,可用于查表 |

地址-目标传送

| LEA reg src | src的EA ➡️ reg |

|---|---|

| LDS reg src | src的(EA+2) ➡️ DS、src的EA ➡️ reg |

| LES | 与LDS类似 |

标志寄存器传送

| LAHF | Load AH from Flags, 标志位第八位读到AH |

|---|---|

| SAHF | 与上反 |

| PUSHF | 标志寄存器入栈 |

| POPF |

Arithmetic

scr和dst必须有一个为reg(scr为im的情况除外

8位无符号数 0~255(FFH(显然16位到FFFF H

显然8位有符号数(80H~7FH即 -128~ +127)、16位 8000H ~ 7FFFH

加减法两个操作数必同为无符号OR有符号

组合BCD:一字节两位 非组合BCD:一字节第四位表示一位

除INC指令不影响CF外,其余均影响CF、OF等六个标志位

调整指令要求操作数为 B, 其他B、W均可

标志位变化

| CF | 无符号溢出 | OF | 有符号溢出❌ | ZF | 运算结果为0时置1 |

|---|---|---|---|---|---|

| SF | 运算结果为负置1 | PF | 运算结果有偶数个1,置1 | AF | 操作数为BCD,半字节进位,置1 |

加法

| ADD | 双精度字先低位ADD,后高位ADC |

|---|---|

| ADC | 带进位,加上CF |

| INC | 修改指针OR循环计数(不修改CF故不用于控制循环结束 |

| AAA | 对非组合BCD调整,结果分为AH、AL存入AX |

| DAA | 组合BCD十进制调整,若超范围则加6调整,默认在AL中进行 |

减法

| SUB | 无借位 |

|---|---|

| SBB | 将低位借的CF减去 |

| DEC | 同INC对CF无影响 |

| NEG | 求补码(0-src)➡️ src 即 (FFH - src)➡️ src,显然src不为0时使CF = 1 |

| CMP | 相减,但结果不送dst,只更改标志位 |

| AAS | 非组合十进制调整,-6 |

| DAS | 组合十进制调整 |

乘法

| MUL src(B or W) | AL*src ➡️ AX 或 AX *src ➡️ DX,AX,无符号 |

|---|---|

| IMUL src | 同上,有符号 |

| AAM | 非组合十进制调整,组合无法调整 |

除法

| DIV src | AX/src ➡️ AL DX,AX/src ➡️ AX 余数➡️AH 或 DX |

|---|---|

| IDIV src | |

| AAD | 非组合十进制调整,组合无法调整 |

| CBW | AL按符号拓展为AX, AL<80H➡️AH=00H 反之AH=FFH |

| CWD | AX ➡️ DX,AX,按符号拓展 |

Logic and Shift

操作数类型均可B 或 W

布尔型指令

| AND | 可用于对指定位屏蔽(清零) |

|---|---|

| OR | 可用于对特定位置1 |

| XOR | 可通过查看ZF比较操作数是否相同 |

| TEST | 与AND类似,只影响标志位 |

| NOT | 取反码 |

| 技巧 | AND AX,AX OR AX,AX XOR AX,AX 都可清CF,但XOR同时清AX TEST AL,01H 可检测AL为奇/偶 |

移位

| SHL/SAL | 低位补0,原高位进CF,高位不等于CF➡️OF=1则符号改变 |

|---|---|

| SHR | 高位补0,原低位进CF |

| SAR | 原高位补高位,低位进CF |

| ROL | 原高位进CF且补低位 |

| ROR | 原低位进CF且补高位 |

| RCL | 原高位进CF,原CF补低位 |

| RCR | 原低位进CF,原CF补高位 |

| 技巧 | 循环指令通过每次检测CF可以判断reg/meg含1或0的个数 |

String Manipulation

串操作使用的寄存器

| SI | 源字符串变址寄存器 |

|---|---|

| DI | 目的字符串变址寄存器 |

| CX | 重复操作次数计数器 |

| AL/AX | SCAS扫描值、LODS的dst、STOS的src |

| DF | 等于0➡️SI、DI自动加1(2);等于1 减 |

| ZF | 扫描、比较串操作终止标志 |

| MOVS/MOVSB/MOVSW | 串传送,要提前将串的变址以及传送长度存入对应reg |

|---|---|

| CMPS/CMPSB/CMPSW | 串比较,根据ZF判断结果(减法) |

| SCAS/SCASB/SCASW | 串搜索,在DI所指串中搜索AL(AX),判断同上 |

| LODS/LODSB/LODSW | 把SI所指串取到AL(AX)中,显然无法使用重复前缀 |

| STOS/STOSB/STOSW | 存串指令 |

| REP/REPZ/REPE/REPNE/REPNZ | CX=0时退出;REPZ/REPE附加ZF条件,等于0提前退出;REPNE/REPNZ同理 |

Control Jump

原理:改变CS与IP

无条件转移、调用、返回

段内转移,目标为NEAR类,近转移,改IP; 段间转移,目标为FAR类,远转移,改CS和IP

| JMP | 可段内直接寻址(JMP NAME PTR TAGET或JMP SHORT OBJECT) 可段内间接寻址(JMP reg或JMP WORD PTR[SI]) 可段间直接寻址(JMP FAR PTR LABEL, LABEL为转移地址号) 可段间间接寻址(JMP DWORD PTR[BX] [SI]) |

|---|---|

| CALL | 调用格式同上 多了保存的功能,分四步 1⃣️ (SP-2)➡️SP;CS ➡️((SP+1),(SP)) 2⃣️SEG➡️CS 3⃣️(SP-2)➡️SP;IP ➡️((SP+1),(SP)) 4⃣️dst➡️IP |

| RET | 恢复栈即SP+4,后面可加立即数加到SP,过程与上面相反 |

条件转移指令

JCC Target 若CC成立则跳转到target

无N时J后两字符为或关系,有N后面字符为与关系

| A | above |

|---|---|

| B | below |

| C | carry |

| E | equal |

| Z | zore(ZF) |

| G | greater(有符号) |

| L | less |

| O | overflow(OF) |

| P | parity(奇偶位PF) |

| CXZ | CX is zero |

| s | sign |

循环控制指令

以CX为计数器,CX不等于0时相当于执行(IP+8)➡️IP

| LOOP | JNZ??? |

|---|---|

| LOOPZ/LOOPE | CX=0或ZF=0均可退出循环 |

| LOOPNZ/LOOPNE | CX=0且ZF=0退出循环 |

Processor Control

状态标志位操作指令

| CF | 进位标志位 | DF | 方向标志位 | IF | 中断标志位 |

|---|

| CLC | CF置0 |

|---|---|

| CMC | CF取反 |

| STC | CF置1 |

| CLD 控制串操作执行(方向 | DF置0 |

| STD 同上 | DF置1 |

| CLI 禁止CPU响应 | IF置0 |

| STI 允许 | IF置1 |

外部同步指令

| HLF | 停机等待外部中断 OR 复位 |

|---|---|

| WAIT | CPU空转状态等待外部中断,完成后返回空转 |

| ESC OPC ,src | 协处理器相关 |

| LOCK | 总线封锁前缀,使LOCK=0 |

空操作指令

| NOP | 占3个时钟周期 |

|---|

Interrupt

中断及终端返回指令

| INT n | n为中断类型号 F、CS、IP入栈,TF、IF清0 取入口偏移地址存入CS、IP |

|---|---|

| IRET | 中断返回指令,F、CS、IP出栈 |

专用中断

| 0 | 除数为0时响应 | 1 | 单步中断,触发条件TF=1 | 2 | 紧急非屏蔽中断NMI | 3 | 断点中断,INT指令触发 | 4 | 溢出中断,INTO指令触发 |

|---|

1 | graph LR |

使用:MASM宏汇编

MASM宏汇编语言规范

分段结构

- 对应CPU内存分段管理

- 每段有名字且以伪指令 SEGMENT 开始,以 ENDS 结束

- 源程序由若干段组成,以 END 结束

语句构成

语句类型

- 指令语句,以助记符为基础

- 伪指令语句,管理性,不产生机器代码

- 宏指令语句

构成与规范

名字域:

- 由字母开头,可包含数字和专有字符

- 指令语句名字后跟冒号,伪指令无

操作符域:

- 主要为助记符

操作数域:

逗号分隔

存储器操作数

- 标号:指令语句的名字域,可认为是指令语句的地址

- 变量:存放在某存储单元的数据,变量符号的地址

表达式:由以上以及运算符组合而成

运算符

算数运算符:完成整数的运算,结果为整数

+、-、*、/ MOD(求余)、SHL、SHR 逻辑运算符

关系运算符

EQ 相等 NE 不等 LT 小于 GT 大于 LE 小于等于 GE 大于等于 分析运算符

SEG 求段基址 OFFEST 求偏移量 TYPE 求变量类型 SIZE 求字节数 LENGTH 求变量长度 TYPE类型值

1 2 4 -1 -2 DB DW DD NEAR FAR 综合运算符

为存储器地址操作数临时指定一个新属性

PTR 将左边类型指定给右边地址 THIS 类似上;与下一条指令分配的段、偏移、属性相同

伪指令

数据定义

DB~DD、DQ、DT

重复操作符 DUP [变量名] DB 100 DUP(?) ?表示不设初值(随机

符号定义

| EQU | 类似于C中#define,不允许重复定义 |

|---|---|

| = | 允许重复定义 |

段定义

段名 SEGMENT [定位类型] [组合类型] [‘类别’]

段内语句

段名 ENDS

- 定位类型:起始边界要求 缺省值PARA

- 组合类型:表示与其他段关系 缺省值NONE

- 类别:一种名字信息

段寻址ASSUME

用来设定各段名与 段寄存器间关系 格式:ASSUME 段寄存器名 : 段名 , 段寄存器名 : 段名 ……

没有给出初值,需和初始化代码配合使用;CS段首址无需初值,系统自动设置

过程定义 PROC/ENDP

格式

1 | 过程名 PROC [NEAR]/FAR(属性) |

程序计数器 $

$的值为程序下一所能分配存储单元的偏移地址

定位伪指令 ORG

指定下一条语句的 偏移地址

结构伪指令

1 | 定义: |

记录伪指令

记录共1~2字节,可为每个字段分配二进制位数

1 | 定义: |

宏相关

1 | 宏定义: |

系统调用功能

见PDF

主存储器

半导体存储器

分类

按读写功能:RWM、ROM (只写、只读

按存取方式:DAM、SAM、RAM (直接存取、顺序存取、随机存取

按器件分类:双极性TTL、单极性MOS

双极性快、功率大、集成度低

单极性相反

按存储原理:RAM、ROM

RAM可读可写、断电丢失

ROM正常只读、断电不丢失

按数据传送方式:并行、串行

性能指标

- 存储容量

- 存取时间

- 功耗

- 工作电源

- TTL +5V

- MOS +3~+18V

组成

- 存储体

- 地址译码器

- 控制逻辑电路

- 数据缓冲器

高速缓存工作原理

- 依赖:

- 程序访问的局部性

- 数据相对集中存储

- 把频繁访问的指令、数据存放在速度非常高 (与CPU速度相当)的SRAM——高速缓存 CACHE中

- 取指令、数据时先到CACHE中查找,没找到再到RAM找

- 系统的平均存取速度(加权平均) ≈ Cache存取速度×命中率+RAM存取速度×不命中率

- Cache与内存的空间比一般为1:128。

存储器寻址方法

片选:根据主存储器 系统对每个存储器芯片的地址范围的分配

字选:选中存储器芯片片内存储单元,由芯片内地译码电路完成

I/O接口

I/O组成

接向CPU

总线驱动器:匹配CPU数据总线速度和驱动能力

地址译码器:接收CPU总线信号并译码,对各端口(reg)寻址

控制逻辑:实现CPU对端口读写操作和时序控制

接向外设

- 缓冲器(数据reg)

- 控制reg:存放CPU控制命令

- 状态reg:保存状态以供CPU查询

I/O控制方式

程序控制

- 无条件传送(同步传送

- 条件:外设必须随时准备就绪

- 条件传送(查询传送

- 先查询外设工作状态,在外设就绪后进行数据输入、输出

DMA控制

中断

三大用途:分时操作、实时处理、故障处理

可屏蔽中断(IF=0时屏蔽

使IF=0情况:

关中断、禁止中断、中断屏蔽

系统复位,使IF=0

任何一个中断被响应,使IF=0

执行指令CLI,使IF=0

使IF=1情况:

- 开中断、允许中断、中断开放

- 执行指令STI,使IF=1

中断向量在中断向量表中的位置称为中断向量地址;

中断向量地址=中断类型号×4

中断子程序使用IRET指令返回

8259A芯片

寄存器

- 中断请求寄存器IRR(8位)

- 保存8条外界中断请求信号IR0~IR7的请求状态

- Di位为1表示IRi引脚有中断请求

- 中断服务寄存器ISR(8位)

- 保存正在被8259A服务着的中断状态

- Di位为1表示IRi中断正在服务中;为0表示没有被服务(处理完毕)

- 中断屏蔽寄存器IMR(8位)

- 保存CPU送来的对中断请求信号IR的屏蔽状态

- Di位为1表示IRi中断被屏蔽(禁止)

优先级分析器PR

- 定义和修改IR0-IR7的优先级别 (通常IR0为高,IR7为最低)

- 同时出现几个中断请求时,根据 优先级别决定处理哪一个

- 处理中断嵌套

工作过程

执行一段CPU的初始化程序, 向8259写命令字,规定8259的工作状态(初始化

中断源通过IR0~IR7向8259A发中断请求,8259A中断请求寄存器IRR的相应位置1

IRR中经中断屏蔽寄存器IMR允许后的置位 进入优先权判别器PR

PR将其中最高优先权的中断请求经控制逻辑向CPU发INT(高电平)请求

若 CPU 处于开中断状态 (IF=1),在当前指令执行结束后,启动中断响应总线操作(发出两个负脉冲作为响应信号)

8259A接收到第一个负脉冲

- 使ISR相应位置1,表示CPU已为该中断请求服务

- 使IRR的相应位清0(防止一次申请的重复处理)

8259A接收到第二个负脉冲

将中断类型号送上数据总线(中断类型号由用户编程和中断请求引脚IRi的序号i共同决定)

CPU读取中断类型号(经响应过程后)进入中断服务程序,直到服务结束返回。

CPU向8259A送中断结束命令作为中断结束标志

若工作在AEOI方式:在第2个INTA#结束时使ISRi复位; 否则由CPU发出EOI命令使ISR i复位

工作方式(5方面)

- 中断优先方式与中断嵌套(各两种

- 中断结束处理方式 (三种EOI命令

- 屏蔽中断源的方式 (两种

- 中断触发方式(两种

- 级联工作方式

通过初始化命令字 (ICW1ICW4) 和操作命令字 (OCW1OCW4) 设置

中断优先方式与中断嵌套

- 中断优先方式

- 固定优先级

- 所有中断请求IRi的中断优先级固定不变

- 优先级排列顺序可编程改变

- 默认优先级顺序从高到低为IR0~IR7

- 循环优先级方式

- 自动中断优先级循环,初始优先级顺序可用编程改变

- 中断请求IRi被处理后,其优先级别自动降为最低, 原来比它低一级的中断上升为最高级

- 固定优先级

- 中断嵌套(中断处理过程中被更高优先级中断)方式

- 普通全嵌套方式(默认

- 中断被处理时,只有更高优先级中断可打断

- 特殊全嵌套方式

- 允许同级或更高优先级打断

- 仅用于多个8259A级连时的主8259A

- 普通全嵌套方式(默认

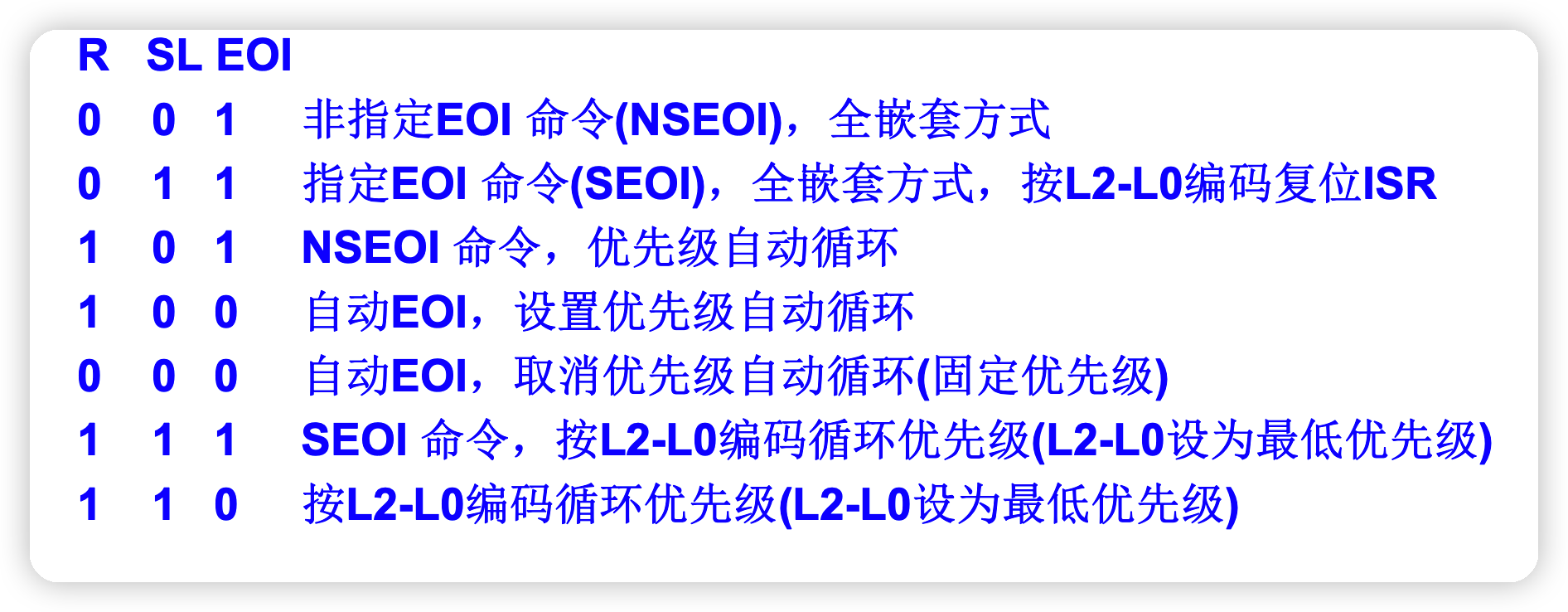

中断结束处理方式

- IRi中断被服务时,ISR中的相应位 ISRi=1,结束后必须清零该位

- 通过向8259A发出中断结束命令 (EOI命令)使ISRi=0(中断结束处理

- 三种EOI命令

- 自动EOI(AEOI)

- 第2个INTA#结束时,由8259A使 ISRi自动复位

- 不用于中断嵌套方式(不保留当前正在服务的中断的状态

- 普通中断结束方式EOI(NSEOI)

- 由CPU发出正常EOI命令

- 使ISRi=1的位中优先级最高的那一位复位

- 特殊中断结束方式EOI(SEOI)

- 由CPU发出一条SEOI命令,指出所要复位的ISR的位号

- 用于特殊屏蔽方式

- 自动EOI(AEOI)

屏蔽中断源的方式

普通屏蔽方式

IMR屏蔽字决定禁止某位IRi所对应的中断:IMi=1 禁止

特殊屏蔽方式

- 假定正在处理IR6,先进入特殊屏蔽方式, 然后设置IM6=1

- 这时除IR6外的所有中断请求均能得到响应

- 只能用特殊中断结束命令结束中断

中断触发方式

边沿触发

IRi上升沿表示有中断请求,触发后可以一直保持高电平

电平触发

在第1个INTA#结束前,IRi必须保持高电平,得到响应之后,输入端必须及时撤出高电平

级联工作方式

- n片8259A可支持7n+1个中断源

- 只能有一片8259A为主片 ➡️ 最多64个中断源

- CAS0-CAS2 链接主从片

- 主SP#/EN# 接高,从接低

- 从INT接主IRi

编程(只考初始化

- 初始化命令字ICW:

- ICW1~ICW4

- 整个系统工作过程中保持不变

- 操作命令字OCW:

- OCW1~OCW3

- 改变初始化的8259A中断控制方式

- 屏蔽某些中断

- 读出8259A状态信息

- 可在初始化之后的任何时刻写入 8259A,并可多次设置

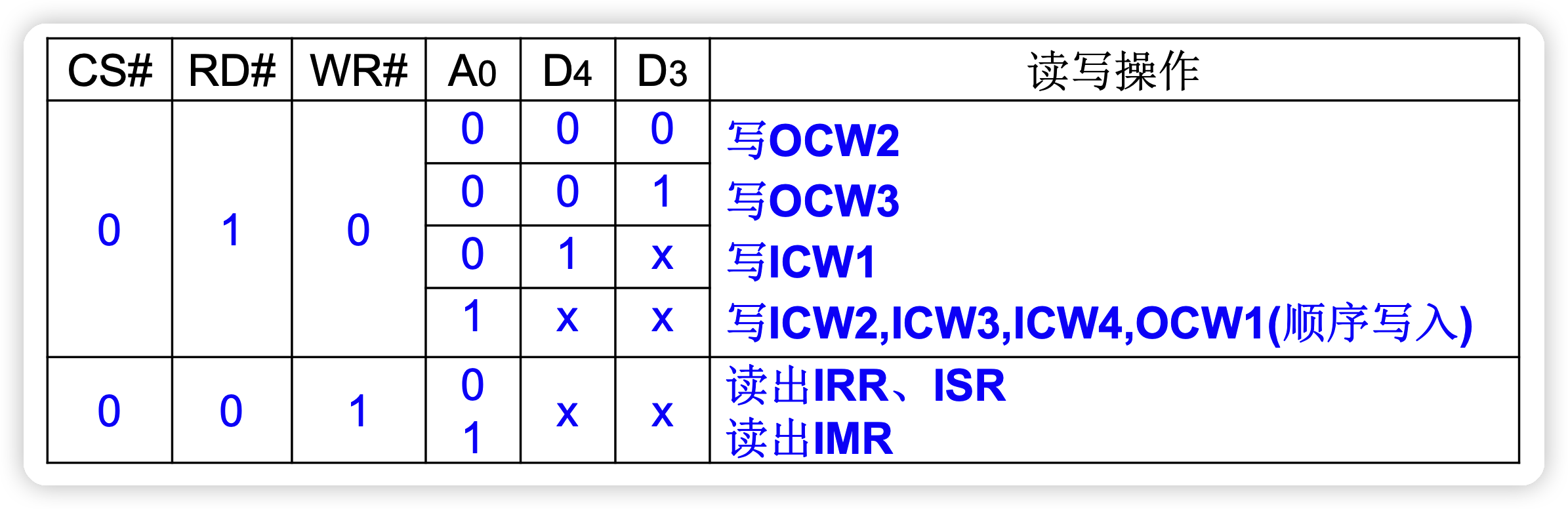

内部寄存器的寻址

- 🌰:

- 接口地址为20H和21H

- MOV DX,20H ;A0=0,写ICW1 等

- MOV DX,21H ;A0=1,写ICW2,OCW1 等

- 记得OUT

初始化

顺序

写 ICW1 ➡️ 写 ICW2 ➡️ (级连写ICW3)➡️ (写ICW4)

ICW1(初始化字: 触发方式、级连控制、ICW4控制)

A0 D7 D6 D5 D4 D3(触发方式) D2 D1(级连控制) D0(ICW4控制) 0 X X X 1 LTIM(1 高电平触发) X SNGL(1 单片) IC4(1 要写ICW4) - 写ICW1意味着重新初始化8259A

- 写入ICW1后,8259A状态:

- ISR和IMR全0

- 中断屏蔽方式:一般屏蔽方式

- 中断结束方式:非自动

- 状态读出逻辑预置为读IRR

- 记:

- 上升沿触发+单片+不写ICW4 ICW1=12H

ICW2(中断向量码)

A0 D7 D6 D5 D4 D3 D2 D1 D0 1 T7 T6 T5 T4 T3 X X X - T7~T3: 中断向量码的高5位

- T2~T0: 中断源的序号,自动填入

- 例 若ICW2命令字为48H,则IR0的中断向量码为 48H,IR7的中断向量码为4FH

- 记:

- IR0 中断向量码 = ICW2

ICW3(级连控制字)

主片

A0 D7 D6 D5 D4 D3 D2 D1 D0 1 S7 S6 S5 S4 S3 S2 S1 S0 - Si=1 对应IRi线上连接了从片

从片

A0 D7 D6 D5 D4 D3 D2 D1 D0 1 0 0 0 0 0 ID2 ID1 ID0 - ID2

ID0 说明连接到主片的哪个IR引脚上;000~111分别对应**IR0IR7**

- ID2

ICW4(中断结束方式字)

A0 D7 D6 D5 D4(SFNM) D3(BUF) D2(M/S) D1(AEOI) D0 1 0 0 0 1 特殊全嵌套方式

0 一般全嵌套方式1 自动EOI方式

0 非自动EOI方式1 BUF M/S 1 1 缓冲方式**/主PIC** 1 0 缓冲方式**/从PIC** 0 X 非缓冲方式**/**正常

操作命令字

写入顺序任意

OCW1必须写入奇地址端口**(A0=1)**

OCW2、OCW3必须写入偶地址端口**(A0=0)**

OCW1(中断屏蔽字)

A0 D7 D6 D5 D4 D3 D2 D1 D0 1 M7 M6 M5 M4 M3 M2 M1 M0 - Mi=1 中断请求线IRi被屏蔽

- 写入IMR寄存器

- A0=1时读OCW1可读出IMR

OCW2(中断结束和优先级循环)

A0 D7(R) D6(SL) D5(EOI) D4 D3 D2 D1 D0 0 =1 优先级自动循环 = 1 SEOI = 0 AEOI 0 0 L2 L1 L0

OCW3(屏蔽方式和读出控制字)

A0 D7 D6(ESMM) D5(SMM) D4(RIS) D3 D2 D1(P) D0(RR) 0 0 = 1

允许特殊屏蔽方式= 1

特殊屏蔽方式置位ISR/IRR选择

(=1读ISR)0 1 =1 查询方式 = 1允许读寄存器

PC机中断程序设计

- 主程序

- 保存原中断向量

- 设置自己的中断向量

- 初始化堆栈指针

- 设置8259A的中断屏蔽字

- STI

- 中断服务程序

- 保存所用到的寄存器内容

- 中断服务程序主体

- 恢复进入时保存的寄存器内容

- 发EOI命令

- STI

- IRET

8255A 并行I/O接口芯片

3个独立的8位并行I/O

- 端口A 常作数据端口,三种工作方式,A组

- 端口B 常作数据端口,两种工作方式,B组

- 端口C 可作数据、状态和控制端口,分两个4位,每位可独立操作(A组控制高4位、B组控低4位

- 可以按位操作,当其工作于 方式0下且作为输出口时,作为输出的位需要设置初始状态(1or0)

分外设接口、内部逻辑、CPU接口三部分

内部寻址

端口A 端口B 端口C 控制寄存器 00(A1A0) 01 10 11 控制字

方式选择控制字: 确定通道的工作方式,给出标识位

D7 D6 D5 D4 D3 D2 D1 D0 1 - D6~D3控制A组

- (D6D5)选择方式0~2

- D4 = 1 A组输入;D3 = 1 C端口(上)输入

- D2~D0控制B组

- D2 选择方式0~1

- D1 = 1 B组输入

- D0 = 1 C端口(下)输入

- D6~D3控制A组

通道C置位**/复位控制字: 控制C**口的输出开关量

D7 D6 D5 D4 D3 D2 D1 D0 0 X X X - (D3D2D1)为C端口位选择,(000) ➡️ 0,(111) ➡️ 7

- D0 = 1 ➡️ 置位

共用一根地址线,使用D7位判断控制字,D7=1表示为方式选择控制字

工作方式

方式0:基本输入输出方式

适用于无条件传送和查询方式的接口电路

- 查询输入输出方式: 把A、B口作为8位数据的输入/输出口,C口的高**/低4位分别定义为A、B**口的控制位和状态位

A口、C口的高4位、B口以及C口的低4位可分别定义为输入或输出,互相独立

输出的口有锁存能力,输入的口则无

C口有按位置位/复位能力

方式1:选通输入输出方式

- 适用于查询和中断方式的接口电路

- 一组选通控制信号控制A端口和B端口的数据输入输出,C位固定用作A、B口的选通控制信号

- A:PC3、PC6、PC7控制,B:PC2~PC0控制;指示两组数据口的状态及选通信号;

- PC4和PC5,用位控方式传送做I/O

- 输入

- STB#——选通信号,将外设数据送入8255的输入锁存器

- IBF——输入锁存器满。通知外设不能送下一个数据。 由STB的前沿产生。CPU用IN指令取走数据后, 信号被清除

- INTR——中断请求。STB#的后沿产生,用于中断 CPU,让CPU读走输入锁存器中的数据

- INTE——中断允许位,是否允许发出INTR请求。INTE =1和IBF为高电平时,允许发出INTR请求

- 输出

- OBF#——通知外设取走数据

- ACK#——外设响应信号,表示已从数据端 口取走数据,使OBF变高

- INTR——ACK#上升沿产生,通知CPU输 出下一个数据(通常接到8259)。

- INTE——中断允许位,INTE=1和OBF#为 高电平时,允许产生INTR信号。

- 数据端口均可设置为输入**/**输出方式,均可锁存

- 中断控制

- 中断允许触发器INTE控制,置位允许中断,复位禁止中断

- 选通输入

- 端口A的INTEA对应PC4

- 端口B的INTEB对应PC2

方式2:双向选通传送方式

- 用于 双向传送数据的外设和 查询和中断方式的接口电路

- 外设通过端口A即可向CPU发送数据,又能从CPU接收数据

- 只适用于端口A,端口B仍按方式0或方式1 工作

- 端口C的PC7

PC3位作为 端口A的控制**/状态信号端口,PC2**PC0用于B组 - 端口A的输入**/输出均有锁存功能;端口A**既可工作于查询方式,又可工作于中断方式

8253可编程计数器/定时器

内部结构和工作原理

计数器:设置好计数初值后,对外部触发脉冲响应减1计数,减为0时,输出结束信号

定时器:设置好定时常数后,对外部时钟信号响应减1计数,按定时常数不断产生时钟周期整数倍的定时间隔

内部总线连接 三个计数器、一个控制字寄存器、一个数据总线寄存器、一个I/O读写

寄存器选择方式

| !CS | !RD | !WR | A1 | A0 |

|---|---|---|---|---|

| 0 | 0(读) | 0(写) | 选择寄存器 | (A1A0) 11时设置控制字 |

外部引线

- 连接系统端

- D7~D0

- 片选

- 读写控制(两个

- A1、A0

- 计数通道

- CLKn 时钟脉冲输入,计数器的计时基准

- GATEn 门控信号输入,控制计数器的启停

- OUTn 计数器输出信号,不同工作方式下产生不同波形(方波、电平或脉冲)

内部计数器

3个计数器相互独立,各自按不同的方式工 作,控制寄存器中的控制字决定其工作方式

每个计数器内部结构相同

- 1个8位控制寄存器(只写

- 1个16位的计数初值寄存器

- 1个16位计数寄存器(减法计数器,计数执行部件

- 1个输出锁存器

控制字

8253必须先初始化才能正常工作,每个计数器都必须初始化一次

初始化8253时,CPU要向8253的控制字寄存器写入一个控制字规定8253的工作方式

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| (D7D6)(00~10) | 计数器选择 | (D5D4)(00~11) | 读写控制 | (D3D2D1) | (000~101) | 工作方式选择 | 0(B计数) 1(D计数) |

| D5D4 | func |

|---|---|

| 00 | 计数器锁存(供CPU读) |

| 01 | 只读**/**写计数器低字节 |

| 10 | 只读**/**写计数器高字节 |

| 11 | 读**/写计数器16**位数 先低字节,后高字节 |

定时**/**计数工作过程

- 设置8253的工作方式

- 设置计数初值到初值寄存器

- 初值 = 产生信号周期*8253时钟频率

- 第一个CLK信号使初值寄存器的内容置入 计数寄存器,以后每来一个CLK信号,计数寄存器减1

- 减到0时,OUT端输出一特殊波形的信号

计数过程中还受到GATE信号的控制

计数启动方式

- 程序指令启动(软件启动

- GATE端保持为高电平

- 写入计数初值后的第2个CLK脉冲的下降沿开始计数

- 外部电路信号启动(硬件启动

- GATE端有一个上升沿

- 对应CLK脉冲的下降沿开始计数

- 计数过程中若GATE出现上升沿,则重新装入原始计数值,重新开始计数

计数过程中读计数值

- 读取当前计数值(计数过程中):

- 先向控制寄存器写锁存命令(即D5D4=00),把当前计数值锁存到输出锁存器

- 再读相应端口数据

- 停止计数器再读

- 用GATE信号使计数器停止

- 规定RL1和 RL0的读写格式后读出

- 读取装入的计数值:

- 直接读取相应的端口

- 分两次读出: 先低字节,后高字节

8253工作方式

Tip:

- GATE出现上升沿时重新装填计数初值

方式 0(软启动): 计数结束产生中断

- 向计数器写完计数值时开始计数,OUT变为0

- 计数到0时OUT输出为1,只计数一次

- GATE为低电平时停止计数

- 在计数时,若重新写入新的计数值,则按新的值重新工作

方式 1 (硬启动): 可重复触发的单稳态触发器(方式0的GATE受控循环

- 设置方式后,OUT即变为高电平

- 写入计数值后,当GATE的上升沿时开始计数,OUT变为低;计数到0后, OUT变高

- 若计数中改变计数值,则要下个硬启动才会以新数计数

方式2(软、硬启动): 分频器(方式1的自动版,可产生周期负脉冲

- 为自动装入计数常数的计数器,计数期间OUT为1, 计数到1后输出1个周期(CLK)的0,并重新装入计数值计数

- 若计数中改变计数值,则要下个周期才会以新数计数(自然的,以周期自动装入常数

方式 3(软、硬启动) : 可编程方波发生器(更改了方式2的OUT占空比

- OUT输出是一个占空比为1:1的方波

- 若计数为奇数,则前面的1比后面的0多1个脉冲

方式 4 : 软件触发的选通信号发生器

- 写入计数值后输出为高,开始计数(OUT)

- 计数结束时,输出1个脉冲低电平,再变高

- 若计数中改变计数值,则要结束后才会以新数计数

方式 5 : 硬件触发的选通信号发生器

写入计数值后由GATE上升沿启动计数

其余与方式4相同